Unifying SerDes Modeling and Signal Integrity Analysis to Accelerate High-Speed Digital Design

As digital systems evolve to support faster data rates and more complex protocols, engineers face growing challenges in ensuring reliable, high-performance communication. High-speed interfaces like PCIe, USB, and DDR demand careful attention to both the design of transmitter and receiver circuits and the integrity of the signals traveling between them. Traditionally, these tasks have been handled in separate workflows—but unifying them can unlock significant advantages.

The Growing Complexity of High-Speed Interfaces

Modern digital interfaces operate at multi-gigabit speeds, where even small imperfections in the signal path can lead to data errors. Signal degradation caused by reflections, crosstalk, jitter, and channel loss becomes more pronounced as data rates increase and eye margins shrink. To manage these effects, engineers must carefully design both the physical channel and the transceiver behavior.

However, these two aspects of the system—transmitter/receiver design and signal integrity analysis—are often developed in isolation. This separation can lead to late-stage surprises, where a design that looks good on paper fails to meet performance targets in hardware.

Interested to learn more? visit our MathWorks Solutions for Semiconductors site, or register to our upcoming Semiconductor Webinar Series

Why Modeling Matters

Accurate modeling is essential for understanding how a high-speed system will behave before it’s built. Engineers use models to simulate how transmitters and receivers interact with the channel, explore design trade-offs, and verify compliance with industry standards.

By modeling the entire system—from the digital logic through the analog front end and across the interconnect—engineers can gain early insight into performance bottlenecks. This system-level perspective helps identify issues such as insufficient equalization, excessive jitter, or poor channel quality long before hardware is fabricated.

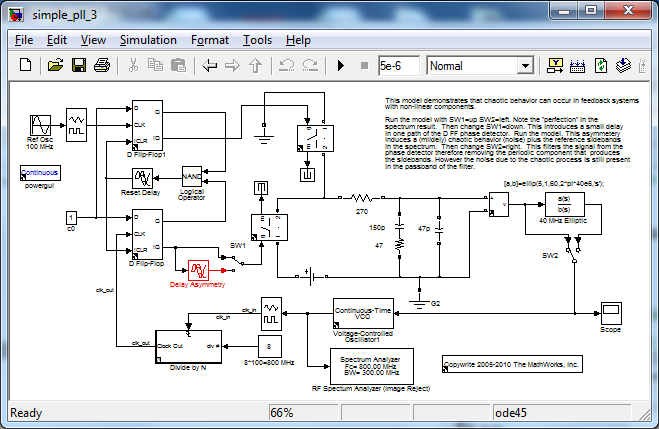

![]()

Figure 1- A unified workflow connects Tx, Rx, & channel modeling, simulations, and signal integrity analysis—enabling faster, more accurate high-speed digital designs.

Signal Integrity: A System-Wide Concern

Signal integrity analysis plays a critical role in ensuring that high-speed signals arrive at their destination with minimal distortion. Engineers use simulation tools to visualize eye diagrams, analyze jitter and noise, and evaluate how different channel configurations affect performance.

This analysis is not just about the physical channel—it also depends on how the transmitter and receiver behave. For example, a receiver with adaptive equalization may compensate for a lossy channel, while a poorly tuned transmitter may introduce excessive jitter. Understanding these interactions requires a holistic view of the system.

![]()

Figure 2 – Signal integrity issues can significantly degrade system performance. Early modeling helps avoid these pitfalls.

The Power of a Unified Workflow

Bringing SerDes modeling and signal integrity analysis into a single environment offers several key benefits:

- Faster Design Cycles: Engineers can iterate quickly, exploring different configurations and identifying optimal settings without switching tools or reformatting data.

- Early Issue Detection: Potential problems can be identified and addressed early in the design process, reducing the risk of costly rework.

- Improved Collaboration: A shared modeling environment fosters better communication between analog, digital, and signal integrity teams.

For example, a team designing a PCIe 6.0 interface can model the transmitter and receiver behavior, simulate the channel using measured or simulated parameters, and evaluate system performance using eye diagrams, bit error rate, or Channel Operating Margin —all within a single platform. This integrated approach streamlines development and improves confidence in the final design.

![]()

Figure 3 – Bringing analog, digital, and signal integrity teams together in a shared modeling environment improves collaboration and accelerates development.

Looking Ahead

As high-speed digital systems continue to evolve, the need for integrated design and analysis tools will only grow. Unifying SerDes modeling and signal integrity analysis is a powerful step toward more efficient, reliable, and scalable design workflows.

In future posts, we’ll explore specific techniques and examples that demonstrate how this unified approach can be applied to real-world designs. In the meantime, try these SerDes examples and signal integrity examples and share your comments and questions below!

Interested to learn more? visit our MathWorks Solutions for Semiconductors site, or register to our upcoming Semiconductor Webinar Series

- Category:

- Semiconductors

Comments

To leave a comment, please click here to sign in to your MathWorks Account or create a new one.