Guided Workflow for Achieving PPA Targets in Integrated Circuit Design

In the world of digital hardware design, translating high-level algorithms into efficient, synthesizable hardware is a critical step. MATLAB® is a popular platform for algorithm development, implementing these algorithms for ASIC requires conversion to hardware description languages and meeting the desired Power, Performance, and Area (PPA) constraints. This blog walks through a modern workflow for converting MATLAB code to synthesizable SystemC and demonstrates how to measure PPA to guide design decisions. SystemC is widely supported by high-level synthesis (HLS) tools, which can further generate RTL code for implementation.

Interested to learn more? Visit our Semiconductor Design and Verification solutions site, or register to our upcoming webinar series.

Workflow Overview

The process typically involves:

- Algorithm Development in MATLAB

- Automated Conversion of MATLAB to synthesizable SystemC using HDL Coder™

- PPA Measurement and Analysis using Cadence® Stratus™ HLS tool

![]()

Let’s illustrate this workflow with an example: AES (Advanced Encryption Standard).

Step 1: MATLAB Algorithm Development

We are using AES example, one of the shipping examples in HDL Coder. Below are the MATLAB code and testbench for the AES example. AES design takes in a plaintext and cipherkey as inputs and produces encrypted output ciphertext. Testbench runs five scenarios to pass the text input and validate the encrypted output by decoding it and comparing with original input text.

![]()

MATLAB simulation results of the design are as below.

![]()

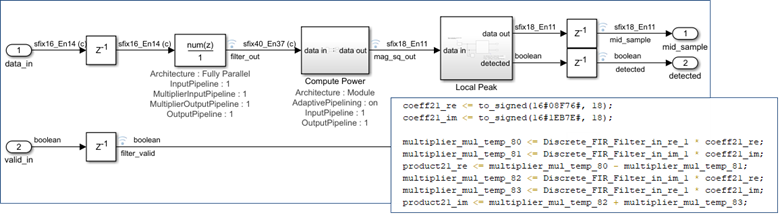

Step 2: Automated Conversion to SystemC

HDL Coder workflow automates the generation of synthesizable SystemC. The typical steps are:

- Select the MATLAB function and testbench for conversion

![]()

- Configure workflow as High Level Synthesis and select HLS tool.

![]()

- Run through code generation and verification steps

![]()

The result is a SystemC project folder containing:

- Synthesizable SystemC source files

- Interface wrappers and configuration files

- Testbenches for functional verification

Step 3: PPA Measurement and Analysis Using HLS Tool

Open the generated SystemC project in Cadence® Stratus™ HLS. This tool allows you to synthesize SystemC code into RTL and simulate the design for functional correctness. By default Cadence® Stratus™ generates three variants of RTL code as shown below.

![]()

A key advantage of this workflow is rapid PPA analysis. Cadence® Stratus™ HLS tool generates detailed reports on:

- Area: Sequential and combinational area, register bits , and more

- Performance: Maximum clock frequency and latency

- Power: Estimated dynamic and static power consumption

PPA figures help you determine if the design meets system requirements or needs further optimization.

Conclusion

Converting MATLAB code to synthesizable SystemC and measuring PPA closes the gap between algorithm development and hardware implementation. This workflow empowers engineers to:

- Prototype and verify algorithms in MATLAB

- Rapidly generate hardware-ready SystemC

- Use HLS tools for synthesis and PPA-driven optimization

By integrating algorithm design, code generation, and PPA analysis, you can accelerate innovation and deliver efficient, high-performance hardware solutions. Refer to these examples and documentation to get started, and share your comments and questions below. You may be excited to try LMS filter example!

Interested to learn more? Visit our Semiconductor Design and Verification solutions site, or register to our upcoming webinar series.

- Category:

- Semiconductors

Comments

To leave a comment, please click here to sign in to your MathWorks Account or create a new one.