HDL Coder Tutorial and Evaluation Reference Guide

Curie’s pick of the week is – actually, make that plural! My picks are the HDL Coder Tutorial and HDL Coder Evaluation Reference Guide, both by Jack Erickson.

If you weren’t aware, you can generate HDL (hardware description language) code from MATLAB and Simulink to program custom FPGA or ASIC hardware. I have worked with customers that are targeting an FPGA for the first time, to customers with decades of ASIC design experience who want to connect their chip design workflow to model-based design to improve their agility and efficiency.

A powerful tool such as HDL Coder means there is a learning curve, especially if you are new to Simulink. To help you get started, the tutorial provides step-by-step instructions on how to take this sample MATLAB code:

% Correlate Rx filter against matched filter FilterOut = filter(CorrFilter, 1, RxSignal); % Find peak magnitude & location [peak, location] = max(abs(FilterOut));

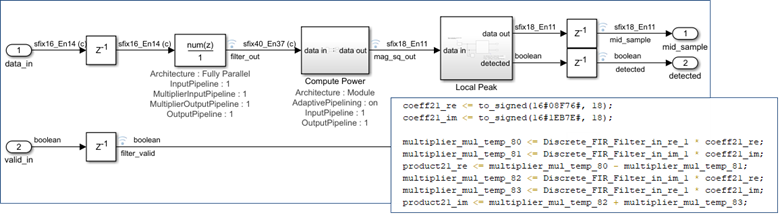

To a Simulink architectural, fixed-point model that is ready to generate VHDL or Verilog:

It is as much about learning the Model-Based Design tools as understanding the process of targeting algorithm designs on FPGA/ASIC hardware.

So you are feeling empowered to start your next HDL design in Simulink after completing the tutorial. But you still have so many questions: “What are the best practices to create efficient hardware?” “How do I direct the tool to use FPGA resources such as RAM and DSP blocks?” “I can’t figure out how to model my clock signal!” (You don’t).

The answers to these questions, and many other popular topics among our users are captured in the HDL Coder Evaluation Reference Guide. The 28-page document describes design patterns and settings that produce efficient HDL code, and highlights useful tools that help speed up your design process.

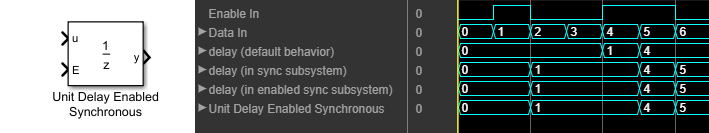

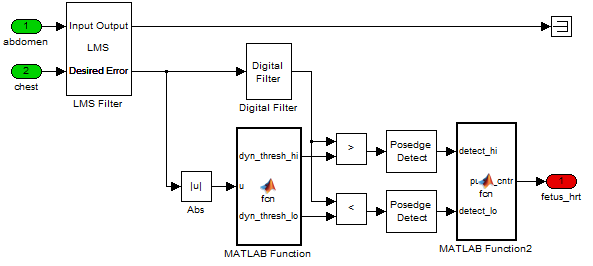

For instance, you will learn how to make local enable signal behave synchronously; view timing diagram with the Logic Analyzer scope; and incorporate MATLAB code in your Simulink design using the MATLAB function block – very handy when it comes to control logic.

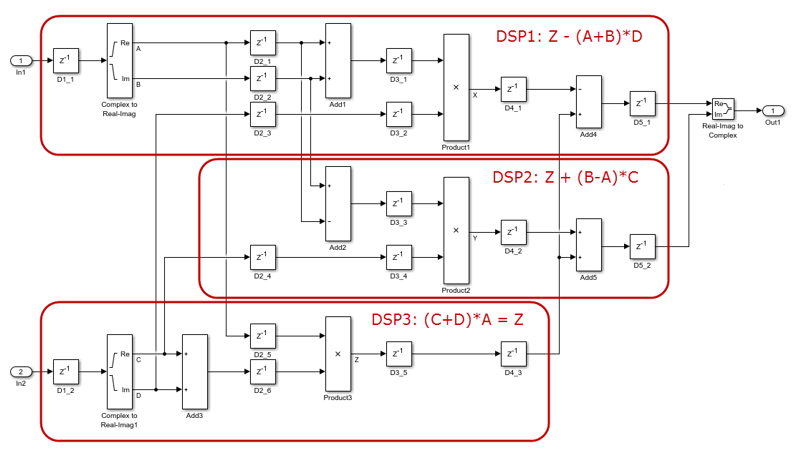

And yes, there is an entire section devoted to FPGA resource mapping, with examples such as this complex multiplier that maps to DSP blocks on Xilinx® and Intel® FPGAs:

So don’t let the number of pages scare you and start reading! (Really, half of them are pictures). And if you want to evaluate capabilities specific to your HDL design, my colleagues and I look forward to working with you.

Give it a try and let us know what you think here!

Published with MATLAB® R2019a

- Category:

- Picks

Comments

To leave a comment, please click here to sign in to your MathWorks Account or create a new one.