What’s New in R2017a!

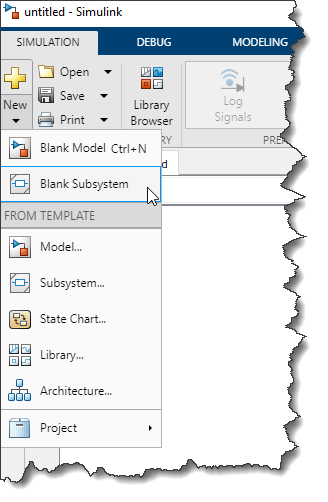

MATLAB R2017a is now available for download. For this first post about R2017a, I want to highlight features that will help you creating models more efficiently.

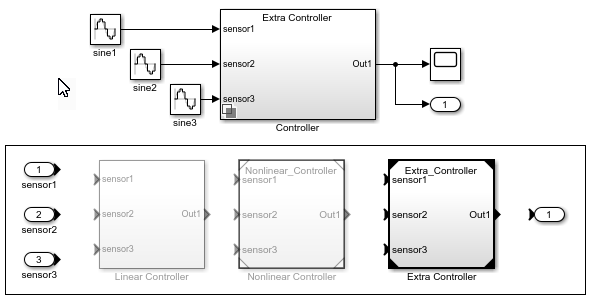

Simplified Subsystem Bus Interfaces

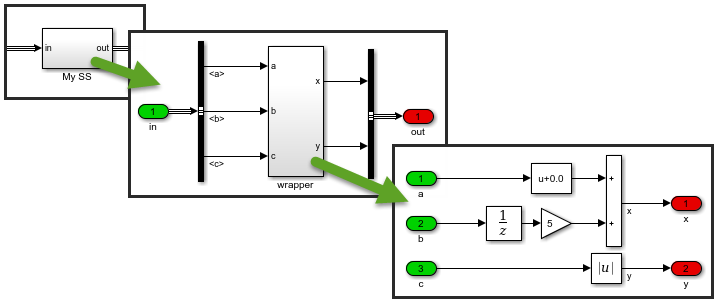

I often receive large models from users where subsystems and buses are arranged like the following. By using a wrapper virtual subsystem, this pattern helps to avoid line cluttering.

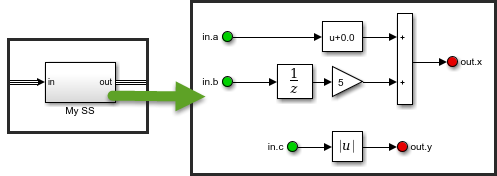

In R2017a, thanks to the new bus element ports, your Subsystems can now look like this:

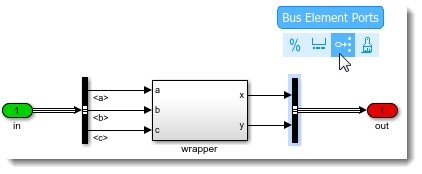

If you want to convert your existing models to this new semantics, we also added a functionality to do the conversion automatically:

Improved Parameterization of Referenced Models

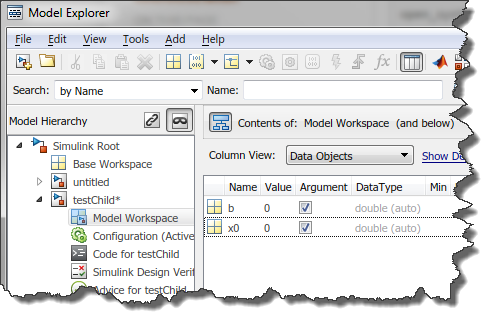

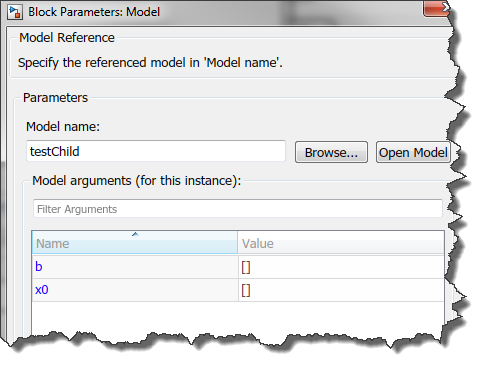

For those of you who need to pass arguments to referenced models, you will notice the new Argument column in the Model Explorer when creating new variables in the model workspace:

When referencing the model, the dialog of the Model block will list the variables marked as Arguments and allow you to specify their value. For those of you with many arguments, notice that the table is searchable and sortable.

Automatic Port Creation

In R2017a, you can simply drag a signal line close to a block and a new port will automatically appear. The best way to describe this feature is to see it in action:

Format Painter

Easily apply the formatting of one block to other blocks using the format painter:

Now it's your turn

Those are some of the features added in R2017a to help you editing model more efficiently. There are many other exciting new features I will be blogging about soon.

Look at the release notes, and let us know in the comments below what is your favorite new feature, or which one you would like to read about on this blog.

- Category:

- What's new?

Comments

To leave a comment, please click here to sign in to your MathWorks Account or create a new one.